### **Cache Design**

#### **Lecture Objectives:**

- 1) Define set associative cache and fully associative cache.

- Compare and contrast the performance of set associative caches, direct mapped caches, and fully associative caches.

- Explain the operation of the LRU replacement scheme.

- Explain the concept of a multi-level cache.

- 5) Explain the three C model for cache.

Least Reconty

- Fully associative cache

A cache structure in which a block can be // placed in any location in the cache.

- Set-associative cache

- A cache that has a fixed number of locations (at least two) where a given block can be placed

#### Direct mapped Set associative designs Set # Data Data Data Comparison of cache Tag Tag Tag Search Search Search

- Working with your partner, solve the following problem

- The following block accesses occur in memory over three different cache structures. Calculate the miss rate for each cache structure

- Structure 1: A direct mapped cache of 4 one word blocks

- Structure 2: A 2 way set associative cache of 4 words

- Structure 3: A fully associative cache of 4 words.

- Access trace: 1, 9, 1, 7, 9, 7, 9, 1, 7, 3

Direct Mapped Example

| Address of<br>memory<br>Access | Hit or<br>miss | 0    | 1                        | 2 | 3         |

|--------------------------------|----------------|------|--------------------------|---|-----------|

| 1"-1                           | 0              |      | *                        |   |           |

| — 1<br>7./ <b>//4</b> ~9       | 6              |      | 9                        |   |           |

| 174 1                          |                |      |                          |   |           |

| 7/47                           | 0              |      | K                        |   | 7         |

| 714 9<br>-07                   | 0              |      | 8                        |   |           |

| <b>→</b> 7                     |                |      |                          |   |           |

| <b>7</b> 9                     | 1              |      |                          |   |           |

| <b>→</b> 1                     | 0              |      |                          |   |           |

| 7                              | -1             |      |                          |   |           |

| <b>4</b> 8                     | 0              | CS27 | 10 Computer Organization |   | <i>'3</i> |

Hit rate i

Hi15 1,7,1 Acresses

3 - 32,

2 Way Set Associative Example

|                                      |                |       |                              |       |       | 1       |

|--------------------------------------|----------------|-------|------------------------------|-------|-------|---------|

| Address of memory Access             | Hit or<br>miss | Set 0 | Set 0                        | Set 1 | Set 1 | 1       |

| /1/2 1                               | M              |       |                              |       |       | 1 UKK 1 |

| 912 9                                | M              |       |                              | 1     | 9     |         |

| 17.2 1                               | Н              |       |                              |       |       |         |

| パ2 <sup>1</sup><br>パ2 <sup>1</sup> 9 | M              |       |                              |       | 7     |         |

| 7/2 29                               | M              |       |                              | 9     | 7     |         |

| -)7                                  | H              |       |                              | ·     |       |         |

| €)9                                  | 1              |       |                              |       |       |         |

| 1/2 1                                | n              |       |                              | 9     |       |         |

| 7.77                                 | h              |       |                              | 7     | Ì     |         |

| 377 3                                | M              |       | CS2710 Computer Organization | 7     | 6 3   |         |

|                                      | HA             | \ =   | H;15                         |       |       | 5       |

|                                      |                |       | total A                      | (1969 | 5     | 10      |

### Any data Anghere Fully Associative Example

| Address of<br>memory<br>Access | Hit or<br>miss | Block 0 | Block 1                  | Block 2 | Block 3 |

|--------------------------------|----------------|---------|--------------------------|---------|---------|

| 1                              | M              | 1       |                          |         |         |

| 9                              | M              | İ       | 9                        |         |         |

| 1                              | Ĥ              |         |                          |         |         |

| 7                              | M              | 1       | 9                        | 7       |         |

| 9                              | И              |         |                          |         |         |

| 7                              | H              |         |                          |         |         |

| 9                              | H              |         |                          |         |         |

| 1                              | H              |         |                          |         |         |

| 7                              | Ħ              |         |                          |         |         |

| 3                              | M              | CS2     | 710 Comput GOrganization | $\neg$  | 73      |

BAND

### associativities

### Direct mapped lake Associativity Data miss rate

| Associativity | Data miss rate |

|---------------|----------------|

| <b>(1)</b>    | 10.3%          |

| 2             | 8.6%           |

| 4             | 8.3%           |

| 8             | 8.1%           |

Diminishing Petun

Computer (Vanization

Associativity OE

Direct Mapped?

Nochoile

Set Associative

- Prefer non valid entry if there is among entries in LRV (Least recently Least) the sext one for Affriximately same performance of LK 62710 Capiter Champaich 955001111

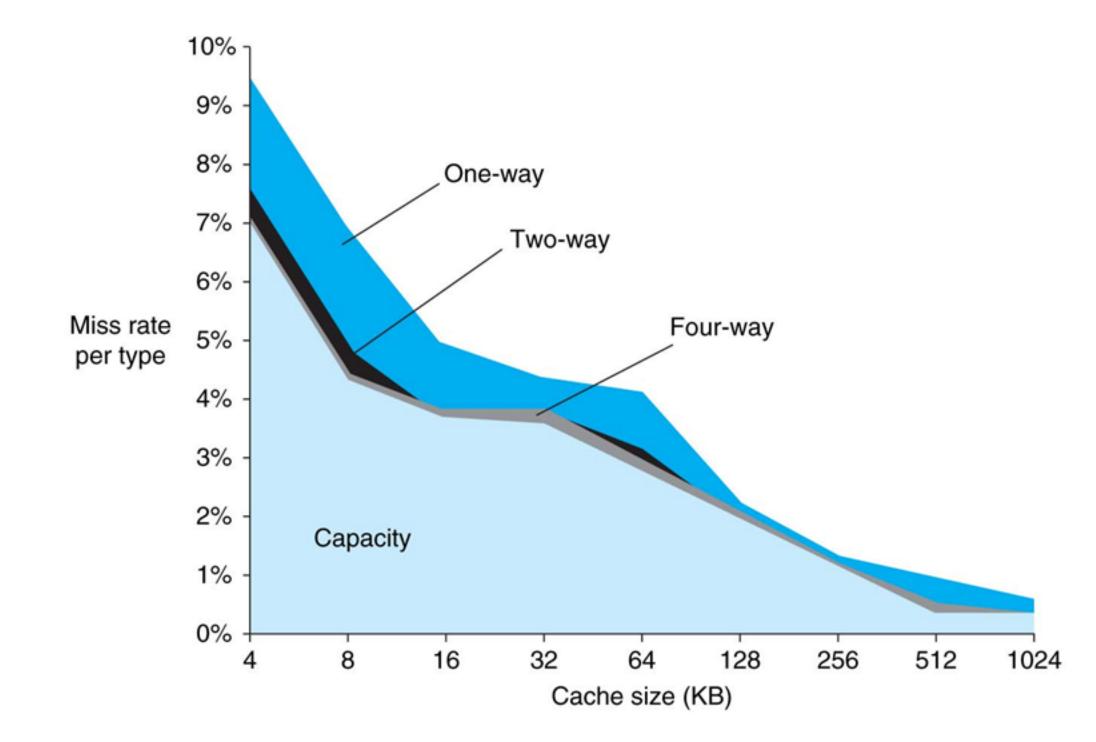

- A Cache model in which all cache misses are classified into one of three categories

- Compulsory Misses

Capacity Misses

Conflict Miss

## Source of misses

Compulsory misses not visible (0.006%)

# Basic Design challenges

| Design Change             | Effect on miss rate                                                                  | Possible negative performance impact                                |

|---------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Increase the cache size   | Decreases capacity misses                                                            | May increase access time                                            |

| Increase<br>Associativity | Decreases miss rate due to conflict misses                                           | May increase access time                                            |

| Increase Block<br>Size    | Decreases miss rate<br>for a wide range of<br>block sizes due to<br>spatial locality | Increases miss penalty. Very large blocks could increase miss rate. |